|

Design of 1 : 8 Demultiplexer Using When - Else Concurrent Statement (Data Flow Modeling Style)-Output Waveform : 1 : 8 Demultiplexer Program----- Title : demultiplexer1 Vhdl program code for 8 to 1 mux You need the tree standar libraries and the function CONV Samples of VHDL Codes Presented in the Examples Below are some of the VHDL codes from the examples in Part II of the book (Chapters 19-25). VHDL code from Example 19.1.   Lesson 2. 0 - VHDL Example 8: 4- to- 1 MUX - case statement. Modelling types are dataflow, behavioral and structural mode. This is placed, routed and produced so that the set of masks create an IC. HDLs form an integral part of electronic design automation (EDA) systems, especially for complex circuits, such as microprocessors, application- specific integrated circuits, and programmable logic devices. In here, we will be using a computer aided design tool. This CAD tool supports many design entry methods like schematic capture, HDL entry, netlist. Once a design has been captured, the next step is to simulate it.

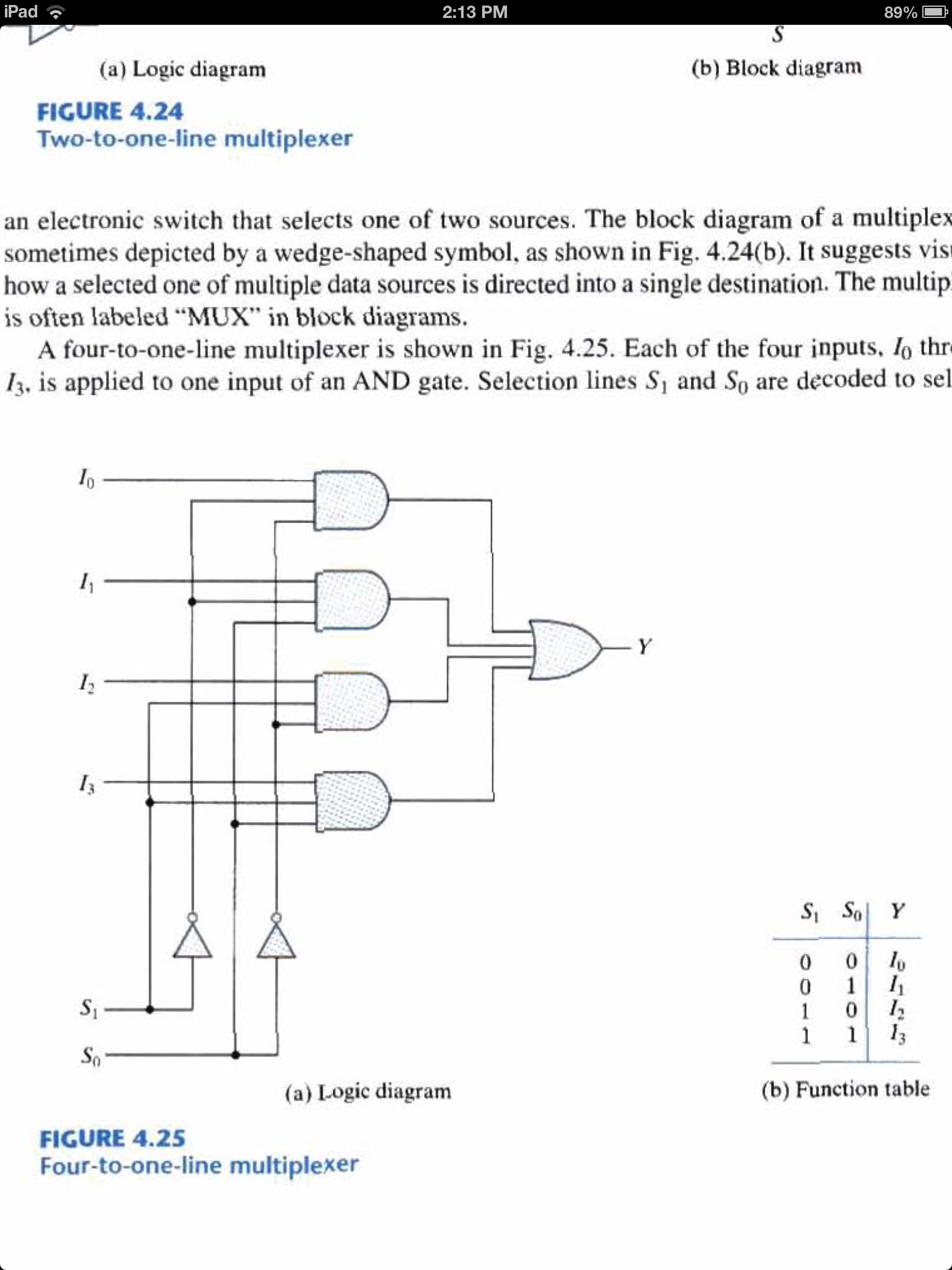

This is done to ensure that the design will meet the requirements of its specification. The first type of simulation that is performed is a Functional Simulation. This is also referred to as a Behavioral simulation in Xilinx Foundation. A behavioral simulation helps to verify the logical behavior of the circuit. VHDL Code----- Title : multiplexer8 Labels: 8:1 multiplexer, 8:1 mux vhdl code, 8:mux, diagram of 8:1 mux, working model of 8:1 mux 4 comments: Unknown said. VHDL CODE: library IEEE. Using VHDL to Describe Multiplexers Objectives Review Multiplexers Learn CASE Statement within Process. We may use a different statement in the architecture body. Using Selected Signal Assignment Statement We have. It helps in the realization of simulations which contains the physical implementation. It does not include any of the timing information. During the synthesis purpose, the CAD will be interpreting the VHDL design information and building blocks which implements design. Many differences in the VHDL description results in different hardware. After the design has been verified, a binary hardware configuration file is generated (bitstream). This file is then downloaded into the FPGA via the JTAG interface. This HDL can be used to model a digital system at different levels of abstraction which ranges from algorithmic to gate level. VHDL language is an integration of different languages like:

VHDL is used to describe the model of a digital hardware. This model gives the external view and one or more internal views.

VHDL provides 5 different primary constructs called design units. They are:

Entity is modeled using the entity declaration and architecture body. Entity declaration tells about the external view of the entity. That is, it tells about the input and output signal names. While the architecture body consists of the internal description of the entity. Consider a half adder circuit below: The entity of the half adder circuit is: Internal details of the entity are specified by the architecture body using the below modeling styles:

It is created by means of an object declaration. An example is: variable COUNT: INTEGER; Each of the data object belongs to one of the classes:

Any object that has constant class holds a single value of a given type. Before the simulation process starts, the value is being assigned to the object and this value cannot be changed while the simulation process takes place.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. Archives

January 2017

Categories |

RSS Feed

RSS Feed